Hi Community!

This project consists of making a full adder using two half adders,you should use a structure in which the two half-adders are joined and creating variables to obtain the adder full end. The port map signals will be used for this projectd since thanks to these can be made the union of half-adders and result in a full adder.

Step 1

We create a new project called FullAdder, in the following screen we choose the type of card to use, in this case it would be the Nexys3 card.

Step 2

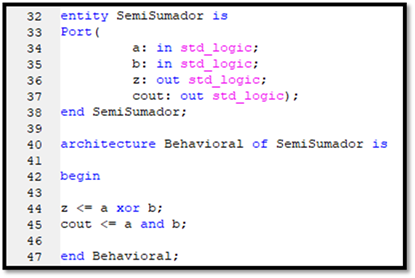

We create a VHDL file to start our activity, as we want To make a full adder using two half adders, we need to first create the semi-adders, we will call it Semi-adder

Step 3

In the VHDL file we introduce the following code:

Knowing previously the basic theory of logic gates we can add these gates, and in turn making logical calculations with the help of the karnaugh map we got. We click on the check syntax to confirm that there is nothing wrong in our code.

Step 4

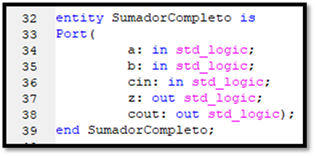

After making our half adder, we create our main program, which also It will be a VHDL module, we will call it FullAdder. After this we begin to make the corresponding logic, it will be seen step by step as this full adder is programmed and how we implement the half adder twice so that it gives us a full adder. We start by adding the inputs and outputs of our adder, which in this case we have two inputs, an input carry, a exit and an exit carry:

Step 5

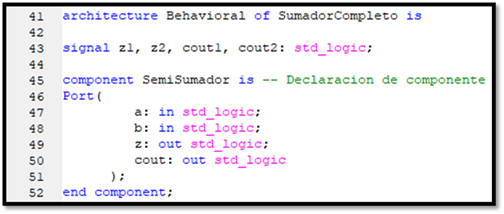

Then we start with the logic and architecture of our program, we add 4 signals (2 z signals and 2 cout signals). Then we create the component which is the same as we create in semi adder, the same variables are added to it:

Step 6

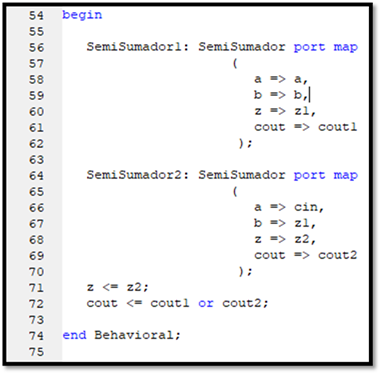

The two half adders are then created from the half adder used as template, with the help of the port map the new variables that each semi adder is going to have, so that the result is adequate:

Step 7

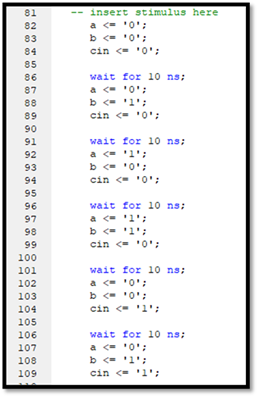

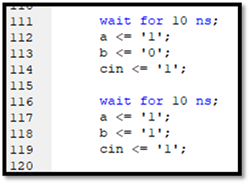

We do the simulation before we can test it on the card to confirm that everything is Ok, for this we choose a new source VHDL Test Bench. And everything is removed have to do with clocks, then after doing this the combinations are applied of the entries: